Classification

Resetsignalsaremainlydividedintotwocategories:synchronousresetsignalsandasynchronousresetsignals.Thesynchronousresetsignalreferstothesignalgeneratedbyresettingtheflip-flopwhentheclockvalidedgearrives;theasynchronousresetsignaldoesnotdependontheclocksignal,andistheresetsignalgeneratedonlywhenthesystemresetisvalid.

Synchronousresetsignal

commoda

1)Conducivetotheanalysisofstatictiminganalysistools

2)CanfilterouttheeffectiveresetsignalGlitchthatlastsshorterthantheclockcycleandhashighanti-interferenceability

3)Itisbeneficialtothesimulationofcycle-basedsimulationtools

Incommoda

1)Theeffectivedurationoftheresetsignalmustbelongerthantheclockcycle,otherwisetheresetsignalmaynotbepickedup

2)Theresetbehaviordependsontheclocksignal.Ifthereisaproblemwiththeclocksignal,theresetbehaviorcannotbecompletedcorrectly

3) Thereisaresetdelayandacombinationallogicdelay

4)Sincethereisonlyanasynchronousresetportinthedevicelibrary,ifasynchronousandasynchronousresetisused,additionalcombinationallogicwillbeinsertedduringsynthesis,whichwilloccupymoreMorelogicresources

Asynchronousresetsignal

commoda

1)Theidentificationmethodissimpleandcanbeusedforglobalreset

2)ThedesignisrelativelySimple,noadditionallogicresources,easytoimplement

3)Mostofthedevicesinthedevicelibraryhaveasynchronousresetports,whichcansaveresources

Incommoda

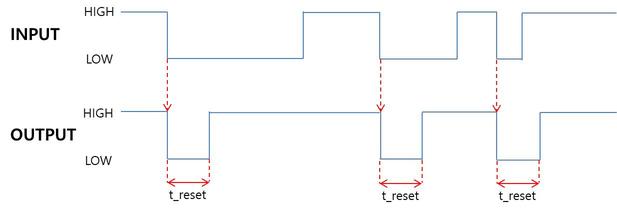

1)Problemsarelikelytooccurwhentheresetsignalisreleased.Iftheresetisreleasedjustnearthevalidedgeoftheclock,itiseasytomaketheregisteroutputmetastable

2)Asynchronousresetiseasytotriggerandissusceptibletoglitches

3)Itisdifficulttoperformstatictiminganalysisandsimulation

Theimportanceofresetsignal

WithintegratedcircuitsWiththedevelopmentofdesigntechnology,thedesignscaleofsingle-chipcircuitsisgettinglargerandlarger,andthedesigncomplexityiscorrespondinglyhigherandhigher.

Atpresent,inthedesignofintegratedcircuits,especiallyinthedesignoflarge-scaleintegratedcircuitsrepresentedbySoCchips(Systemonchip),synchronoustimingdesignmethodsareusuallyadopted.Thatis,allflip-flopsinsidethechipworkonthesameclocksignal,andtheflip-flopstatealsooccursatthesametime.

Thesynchronoustimingdesignmethodrequiresthattheinternalclocksignalofthechiparrivesatthesametimeforeachflip-flopinsidethechip.Infact,duetothedifferentpathsoftheclocksignaltoeachflip-flop,thedelayoftheclocksignaloneachflip-flopwillnotbeconsistent.Inordertoensurethatthetimeatwhichtheclockedgereacheseachflip-flopisthesame,designersusuallyneedtocompensateforeachpaththattheclockgoesthrough,thatis,tobalancetheclocktree.

Similarly,inthedesignofthechipresetcircuit,thedelayoftheresetsignalwillalsoaffectthedigitallogicofthecircuit.ThecircuitshowninFigure1,becausetheresetsignalinputterminals(Rst)ofthreedifferentcircuitmodulesandtheresetsignalsource(Reset)oftheentirechiphavedifferentconnectionpaths,itmaycauseTheresetsignaldelayasshowninFigure2.Whentheresetsignalisnotsynchronized,becausetheoutputofeachmodulehassubsequentlogicoperations,itmaycausetheresetoperationofmodule2andmodule3tobestillnotcompletedatthemomentwhentheresetsignalofmodule1disappearsandstartstorun.Itisstillinanuncertainstate,whichleadstotheundesirableresultoftheconfusionofthelogicstateofthesystem.