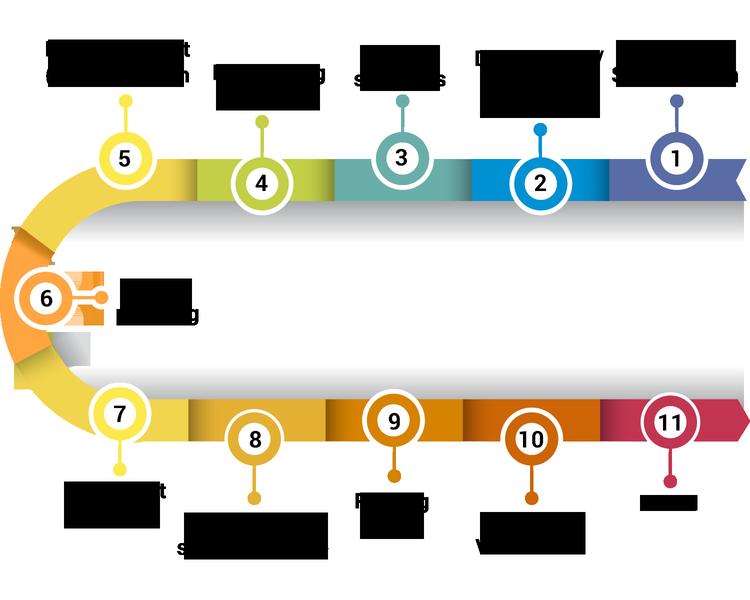

Suunnittelu sisältää

Theflowofintegratedcircuitdesigngenerallyfirstneedstobedividedintosoftwareandhardware,andthedesignisbasicallydividedintotwoparts:chiphardwaredesignandsoftwareco-design.Chiphardwaredesignincludes:

1. Toiminnallinen suunnitteluvaihe.

Designer’sproductapplicationoccasions,setsomespecificationssuchasfunction,operatingspeed,interfacespecifications,environment

environmenttemperatureandpowerconsumption,etc.,asafuturecircuitdesigninaccordancewith.Itcanfurtherplanhowsoftwaremodulesandhardwaremodulesshouldbedivided,whichfunctionsshouldbeintegratedintheSOC,andwhichfunctionscanbedesigned

laskea piirilevyltä.

2. Suunnittelun kuvaus ja käyttäytymistason tarkastus

Afterthefunctiondesigniscompleted,theSOCcanbedividedintoseveralfunctionalmodulesaccordingtothefunction,andtheIPcoresthatwillbeusedtoimplementthesefunctionsaredetermined.

ThisstageindirectlyaffectstheinternalstructureoftheSOCandtheinteractivesignalsbetweenvariousmodules,aswellasthereliabilityoffutureproducts.

Afterdecidingthemodule,youcanusehardwaredescriptionlanguagesuchasVHDLorVerilogtorealizethedesignofeachmodule.

Then,usethecircuitsimulatorofVHDLorVerilogtoverifythedesign(function

simulointi tai käyttäytymisen simulointi).

Notethatthiskindoffunctionalsimulationdoesnotconsidertheactualdelayofthecircuit,norcanitobtainaccurateresults.

3. Logistiikkasynteesi

Afterconfirmingthatthedesigndescriptioniscorrect,youcanusethelogicsynthesistool(synthesizer)forsynthesis.

Inthesynthesisprocess,youneedtoselecttheappropriatelogiccelllibraryasareferencewhensynthesizinglogic

piirit.

Thewritingstyleofthehardwarelanguagedesigndescriptionfileisanimportantfactorthatdeterminestheexecutionefficiencyofthesynthesistool.

Infact,theHDLsyntaxsupportedbysynthesistoolsislimited,andsometooabstractsyntax

isonlysuitableasasimulationmodelforsystemevaluationandcannotbeacceptedbysynthesistools.

Logisynteesi saa porttitason verkkoluettelon.

4. Gate-LevelNetlistVerification

Gate-LevelNetlistVerificationisaregistertransfer-levelverification.Themaintaskistoconfirmwhethertheintegratedcircuitmeetsthefunctionalrequirements.Thistaskisgenerallycompletedwithagate-levelverificationtool.

Notethatthedelayofthegatecircuitneedstobeconsideredinthesimulationatthisstage.

5. Layoutanddrouting

Layoutreferstorationallyarrangingthedesignedfunctionalmodulesonthechipandplanningtheirlocations.Wiringreferstothewiringthatcompletestheinterconnectionbetweenmodules.Notethattheconnectionbetweeneachmoduleisusuallyrelativelylong,sotheresultingdelaywillseriouslyaffecttheperformanceoftheSOC,especiallyinthe0.25micronprocessandabove,thisphenomenonismoresignificant.Atpresent,thisindustryisstillavacancyinChina,andtherearestillrelativelyfewuniversitiesofferingintegratedcircuitdesignandintegratedsystems.Amongthem,schoolswithbetterteachersincludeShanghaiJiaotongUniversity,HarbinInstituteofTechnology,HarbinUniversityofScienceandTechnology,SoutheastUniversity,andXi’anElectronicTechnology.University,UniversityofElectronicScienceandTechnologyofChina,FudanUniversity,EastChinaNormalUniversity,etc.Thisfieldhasgraduallybecomesaturated,andthereisagrowingtrendtofollowthepathofthesoftwareindustryinthosedays.

Suunnitteluprosessi

1.Circuitdesign

Completethecircuitdesignaccordingtothecircuitfunction.

2. Esisimulaatio

Simulationofcircuitfunctions,includingsimulationofpowerconsumption,current,voltage,temperature,voltageswing,inputandoutputcharacteristicsandotherparameters.

3. Layoutdesign (Asettelu)

Drawthelayoutbasedonthedesignedcircuit.Cadencesoftwareisgenerallyused.

4. Jälkisimulaatio

Simulatethedrawnlayoutandcompareitwiththeprevioussimulation.Ifitfailstomeettherequirements,thelayoutneedstobemodifiedorredesigned.

5. Jatkokäsittely

TheGDSIIfileisgeneratedfromthelayoutfileandsubmittedtoFoundryfortape-out.