Компютърно въведение

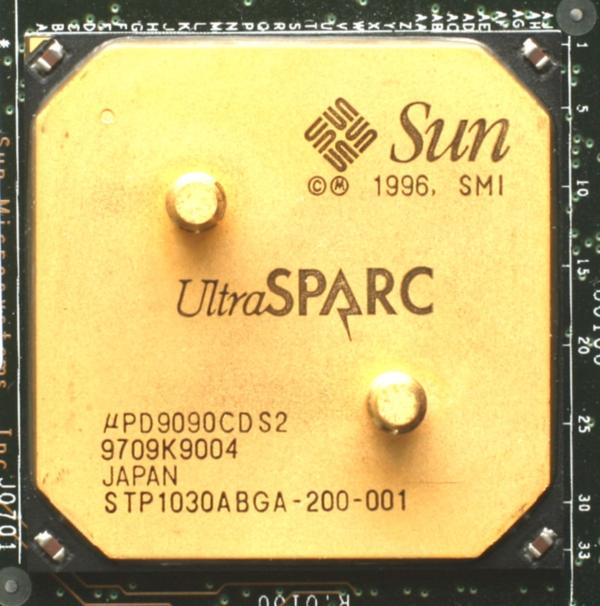

ReducedInstructionSetComputing(RISC:ReducedInstructionSetComputing)isacomputerwithashorterinstructionlength,anditsoperatingspeedFasterthanCISC.RISCandCISCareCPUsthatcanbedividedintotwocategoriesfromthecharacteristicsoftheinstructionset:CISCandRISC.RISCistheabbreviationofEnglishReducedInstructionSetComputing,whichis"reducedinstructionoperationset",CISCis"complexinstructionoperationset".TheinstructionsystemofRISCisrelativelysimple.Itonlyrequiresthehardwaretoexecuteverylimitedandmostcommonlyusedinstructions.Mostofthecomplexoperationsusematurecompilationtechnologyandaresynthesizedbysimpleinstructions.Atpresent,theCPUofthisinstructionsystemiscommonlyusedinmiddleandhigh-endservers,especiallythehigh-endserversallusetheCPUoftheRISCinstructionsystem.TheCPUsthatuseRISCinstructionsinmid-to-high-endserversmainlyincludeAlphafromCompaq(Compaq,thenewHewlett-Packard),PA-RISCfromHP,PowerPCfromIBM,MIPSfromMIPS,andSparcfromSUN.

RISCisrelativetothecomplexinstructionsetcomputer(CISC).Theso-calledcomplexinstructionsetcomputerreliesonincreasingthehardwarestructureofthemachinetomeettheincreasingperformancerequirementsofthecomputer.Thedevelopmentofcomputerstructurehasalwaysbeenmonopolizedbyprocessorswithincreasingcomplexity.Inordertoreducethedifferencebetweencomputeroperationsandhigh-levellanguages,inordertoimprovetheoperatingcharacteristicsofthemachine,therearemoreandmoremachineinstructionsandmoreandmorecomplexinstructionsystems..Especiallythecontradictionbetweentheearlierhigher-speedCPUandtheslower-speedmemory.Inordertominimizethenumberofaccesstodataandincreasethespeedofthemachine,acomplexinstructionsethasbeengreatlydeveloped.However,withthedevelopmentofsemiconductorprocesstechnology,memoryThecontinuousincreaseinspeed,especiallytheuseofhigh-speedbuffers,hascausedfundamentalchangesinthecomputerarchitecture.Whilethehardwaretechnologyhasimproved,thesoftwarehasalsoundergoneequallyimportantdevelopments,andoptimizedcompilershaveappearedtoenabletheexecutionofprograms.Timeisreducedasmuchaspossible.Andtominimizethememoryoccupiedbymachinelanguage,withadvancedmemorytechnologyandadvancedcompilerconditions,theCISCarchitectureisnolongerapplicable,sotheRISCarchitecturewasborn.ThebasicstartingpointoftheRISCtechnologyistoadoptReducethemachineinstructionsystemtoreducethecomplexityofhardwaredesignandincreasethespeedofinstructionexecution.InRISC,thecomputeractuallyexecutesinstructionsineverymachinecycle.Nomattersimpleorcomplexoperations,theyareallcompletedbyprogramblocksofsimpleinstructions,whichhasstrongsimulationcapabilities.

InaRISCmachine,itisrequiredtoexecuteallinstructionswithina"singlemachinecycle"time,andthemostfundamentalthroughputlimitofthesystemisdeterminedbytheproportionofthememoryaccesstimeduringprogramoperation.Therefore,aslongasTheCPUexecutiontimeisthesameastheinstructionfetchingtime,andthemaximumsystemthroughputratecanbeobtained.(Foramachinecycletoexecuteaninstruction).InRISCmachines,hardwarecontrolisusedtoachievefastinstructiondecoding,andfewerinstructionsandsimpleaddressingmodesareadopted,andinstructiondecodingandhard-wiredcontrollogicaresimplifiedthroughafixedinstructionformat.Inaddition,RISCdesignisbasedoncomplexcompilationdesignoptimizationtoobtainasimplehardwarechipenvironment.CompileroptimizationcanimprovetheoperatingefficiencyofHLLprograms,butallprogramsmustbewritteninhigh-levellanguages.

RISCdesigneliminatesmicrocoderoutines,andhandsthelow-levelcontrolofthemachinetosoftware.Thatis,usingfasterRAMinsteadofthemicrocodeROMintheprocessorastheinstructioncache(Cache),thecomputer'scontrolresidesintheinstructioncache,sothattheinstructionstreamgeneratedbythecomputersystemandthecompilercanmeettherequirementsofhigh-levellanguageandhardwareperformanceWorkcloselytogether.

Theperformanceofacomputercanbemeasuredbythetimerequiredtocompleteaspecifictask,whichisequaltoC×T×I.

C=броят цикли, необходими за изпълнение на всяка инструкция, T=времето на всеки цикъл, I=броят инструкции за задача

RISCtechnologyistomakeCandTMinimized,thereductionofCandTmayleadtoanincreaseinI,buttheuseofoptimizedcompilationtechniquesandothertechnologiescanmakeupfortheimpactoftheincreaseinIonmachineperformance.ThereasonwhyRISCtechnologyhasrapidlydevelopedfromanewinsightintoapromisingcomputermarketismainlyduetothefollowingreasons:oneisthattheRISCstructureadaptstotherapiddevelopmentofVLSItechnology;theotheristhatRISCsimplifiestheprocessorstructure,implementationanddebuggingItiseasier,sothedesigncostislow,andthedevelopmentcycleisshort;thethirdistosimplifythestructure,andtheprocessoroccupiesasmallerchiparea,sothatlargerregisterfilescanbeintegratedonthesamechip,translationbackupbuffer(TLB),Coprocessorsandfastmultipliersanddividers,etc.,enabletheprocessortoobtainhigherperformance;fourth,RISC'ssupportforHLLprogramsisbetterthanpreviouscomplexinstructionsystemcomputers,allowingusers(programmers)toeasilyuseaunifiedinstructionset.Itiseasytoestimatetheeffectofcodeoptimization,sothatprogrammershavemoreconfidenceinthecorrectnessofthehardware.

Класификация

Използване на многостепенна инструкция тръбопроводна структура

UsingpipelinetechnologycanmakemultipleinstructionsoverlapexecutionateverymomenttoreducethevalueofCPI,SothattheCPUdoesnotwasteemptycycles.Example:PentiumⅡ/Pro/Celeroncanissueandexecutefiveinstructionsatthesametime,AMD-K6/K6-2canissuesixinstructionsatthesametime.

Simpleinstructionsandsomecomplexinstructionswithhighfrequencyinthemachine

ThiscanreducethenumberofclockcyclesandincreasetheCPUspeed.TheessenceistoreducethevalueunderCPI.Example:Choosearithmeticinstructions,load,storeinstructions,andtransferinstructionsasthemaininstructionset.

Използване на LoadandStorestructures

OnlytheLoadandStoreinstructionsareallowedtoperformmemoryoperations,andtherestoftheinstructionsalloperateonregisters.Examples:Amd-K6/K6-2,PⅡ/Celeron/Proallsupportdirectoperationandrenamingofregisters,andgreatlyincreasethenumberofgeneral-purposeregisters.

Инструкции за забавено зареждане и инструкции за прехвърляне

Becauseofthespeeddifferencebetweenthetwodatafromthememorytotheregister,thetransferinstructionsneedtocalculatetheentryaddress,whichgreatlylimitstheexecutionspeedoftheCPU.Therefore,inordertoensurethehigh-speedoperationofthepipeline,RISCtechnologyallowsanirrelevantimmediatelyexecutableinstructiontobeaddedbetweenthemtoincreasethespeed.

Пример: Отразено главно в предсказуемо изпълнение, непоследователно изпълнение и предаване на данни и т.н., с изключение на IntelP54/55C не поддържа, като K6-2, PⅡподдържа.

Използване на структура на acache

InordertoensuretheuninterruptedtransmissionofinstructionstotheCPUarithmeticunit,theCPUhassetupacertainsizeofCachetoexpandthebandwidthofthememoryandmeettherequirementsoffrequentCPUfetching.Referstorequirements,generallytherearetwoindependentCaches,whichstore"instructions+data"respectively.

Пример:PⅡ/Celeron:16K+16K,AMD-K6/K6-2 е 32K+32K,CyrixMⅡ:64K(всъщност два 32KCache,това се използва като споделен кеш),PⅡсъщо добавя L2Cache,което значително подобрява скоростта на процесора.

Характеристики на RISC

ThefeaturesofRISCarethattherearefewinstructionsandformats,simpleoperationandcontrol.Specifically,therearethefollowingaspects.

Опростен набор от инструкции

TheRISCstructureadoptsasimplified,long-shortinstructionset,whichenablesmostoperationstoobtainthehighestpossibleefficiency.Someoperationsthatneedtobeimplementedwithmulti-cycleinstructionsinthetraditionalstructurearereplacedbymultiplesingle-cycleinstructionsintheRISCstructurethroughmachinelanguageprogramming.ThesimplifiedinstructionsethasgreatlyimprovedtheperformanceoftheprocessorandpromotedthedesignofRISC.Thereisnodefiniteanswertothequestionofhowsimpleitis.ComparingtheexistingRISCsystemwiththeCISCsystem,wecanseethegeneralsituation.Generally,forRISC:

Тогава броят на инструкциите е малък, не повече от 128.

Има няколко режима на адресиране, не повече от 4 вида.

Има няколко формата на инструкции, не повече от 4 типа.

Itisveryprudenttodealwiththesuggestionsontheexpansionoftheinstructionset.Itmustbecarefullyweighedandverifiedtoseeiftheycanreallyimprovetheperformanceofthecomputer.Forexample,MIPSadoptsarule:addinganinstructionmustmaketheperformancegain1%withinacertainapplicationrange,otherwisethisinstructionwillberejected.

Инструкция часовников цикъл, дължина на инструкцията е равно

Ifthetasktobeexecutedbyeachinstructionissimpleandclear,thetimerequiredtoexecuteeachinstructioncanbecompressedorreducedbythenumberofcycles.ThedesigngoalofRISCistoimplementamachinecycletoexecuteaninstruction,makingthesystemoperationmoreefficient.Technologiesthatapproachthisgoalincludeinstructionpipelinesandspecificinstallation/storagestructures.Atypicalinstructionmayincludethestagesoffetching,decoding,executing,andstoringresults.Single-cyclemeanscanbeachievedbymakingallinstructionsthestandardlength.Thestandardinstructionlengthshouldbeequaltothebasicwordlengthofthecomputersystem,usuallyequaltothenumberofdatalinesinthesystem.

Inanyinstructionfetchcycle,acompletesingleinstructionmustbepassedtotheCPU.Forexample,ifthebasewordlengthis32bitsandthedataportionofthesystembusis32lines,thestandardinstructionlengthis32bits.Itisdifficulttomaketheexecutiontimeofallinstructionsconsistent.Someinstructions,includingsimplelogicoperationsonCPUregisters(clearingregisters,etc.),canbeeasilyexecutedwithinoneCPUclockcycle;otherinstructionsmayincludememoryaccess(readingandwritingtomemory,fetching,etc.)orMulti-cycleoperations(multiplication,division,etc.)maynotbeexecutedinasinglecycle.Thisputsforwardsucharequirementtothedesigner;allowsmostfrequentlyusedinstructionstobeexecutedinasinglecycle.

Тръбопровод с инструкции

Thewaytoreducethenumberofcyclesrequiredtoexecuteaninstructionistoexecutemultipleinstructionsoverlapped.Theinstructionpipelineusessuchaworkingmethod:theexecutionofeachinstructionisdividedintoseveraldiscreteparts,andthenmultipleinstructionsareexecutedatthesametime.Thefetchandexecutionphasesofanyinstructionoccupythesametime,ideallyasinglecycle.ThiscanbesaidtobethemostimportantdesignprincipleofRISC.AllinstructionsexecutedfromthememorytotheCPUfollowaconstantflow.Eachinstructionisexecutedatthesamepace,nowaitinginstructions.TheCPUisalwaysbusy.Thenecessaryconditionstoachievepipelineoperationare:

Standard,fixed-lengthinstructions,whichareequaltothewordlengthofthecomputerandthewordlengthofthedataline.

ThestandardexecutiontimeofallinstructionsispreferablywithinasingleCPUcycle.

Forexample,theSPARCchipadoptsafour-stagepipelinestructureforfetching,decoding,executingandwritingresultstomaximizeprocessorperformance.Atthebeginningofeachclockcycle,anewinstructioncanbeexecuted,whichensuresthatanewinstructionisfetchedfromthememoryineachmachinecycle.Therefore,ingeneral,mostinstructionscanbeexecutedinasinglecycle.accomplish.Тръбопровод с инструкцииtechnologycanbecomparedtoanassemblyline-instructionsarelikeprocessedproducts,fromoneprocesstothenext,untilitisexecuted.

Therefore,itispossiblefortheinstructionpipelinetouseafactorequaltoitspipelinedepthtoreducethenumberofinstructioncycles,butinthiscase,itisrequiredthatthepipelineisalwaysfilledwithusefulinstructionsandnothingpreventsinstructionsfrompassingthroughthepipeline.Demandputsacertainburdenonthestructure.Forexample,competitionforresourcessuchasALUpreventstheflowofinstructionsinthepipeline.Theundesirableconsequencescausedbytheexecutiontimeofdifferentlengthsareevenmoreobvious,whichiswhyRISCdefinesaninstructionsetwiththecharacteristicsdescribedabove.

Структура Loadandstore(LOAD/Store).

Toexecutememory-relatedoperationinstructions,itisnotrequiredtoincreasethetimeofeachcycleorthenumberofcyclesofinstructions.Oneofthetwomustbechosen.Becausetheseinstructionsneedtocalculatetheaddressoftheoperand,readtherequiredoperandfromthememory,calculatetheresult,andthensendtheresultbacktothememory,theirexecutiontimeismuchlonger.Inordertoeliminatethenegativeeffectsofsuchinstructions,RISCadoptssuchaloadandstorestructure:onlyLoadandStoreinstructionscanaccesstheinter-memory,andallotheroperationsonlyaccesstheregistersstoredintheprocessor.Theoperandin.Itsadvantagesare:

Reducethenumberofaccessestomemoryandreducetherequirementsformemorybandwidth.

Alloperationsarerestrictedtoregistersonly,whichhelpssimplifytheinstructionset.

Cancelingmemoryoperationsmakesiteasierforthecompilertooptimizeregisterallocation—thisfeaturereducesmemoryaccessandalsoreducesthenumberofinstructionspertask.

AllthesecontributetoRISC'sgoalofexecutingoneinstructionpercycle.Nevertheless,loadandstoreinstructionsstillhindertherealizationofIRSC'sdesigngoals.Theuseofoptimizedcompilationtechnologytodealwiththedelayofloadinstructionsandbranchinstructionscanhelpsolvetheproblem.AlthoughoptimizingcompilationtechnologyisnotspecificallyorientedtoRISCstructures,optimizingcompilersrelyonRISCstructurestocompletetheiroutstandingtasks,andRISCstructuresrelyonoptimizingcompilerstogettheirbetterperformance.Theinterpretermustbeabletoanalyzethedataandcontrolflow,andadjusttheorderofexecutionofinstructionsonthisbasis,andcleverlyarrangetheusageofregisters.TheformerfunctioncanreducetheidletimeoftheCPU,andthelatterfunctioncanincreasethereusabilityrateofthedatastoredintheregister,reducethenumberofmemoryaccesses,andshortenthelengthofthedatapath.

Имате по-голям регистър

Inordertofacilitatetherealizationoftheoperationofmostinstructionsbetweenregisters,thatis,theso-calledregister-to-registeroperation,theremustbeasufficientamountofCPUgeneral-purposeregisters.AsufficientamountofregistersmakesitnecessarytotemporarilystoretheintermediateresultsforoperationsintheCPUregistersinsubsequentoperations,thusreducingtheloadingandstoringofthememory,andspeedinguptheoperation.Atleast32general-purposeCPUregistersareusedinindustrializedRISCsystems.

Използване на твърд кабелен контрол

Duetotheflexibilityprovidedbymicroprogrammingtodesigners,manyCISCsystemsarecontrolledbymicroprogramming.Differentinstructionsusuallyhavedifferentlengthsofmicroprograms,whichmeansthatthenumberofcyclesexecutedbyeachinstructionisdifferent,whichcontradictstheconsistentandstreamlinedprocessingprincipleofallinstructions.Butthiscanbesolvedbyhard-wiredcontrol,andthespeedwillbefaster.Therefore,RISCshouldbecontrolledbyhard-wiredwires.Theremaybeexceptionswheneachinstructionhasaone-to-onecorrespondencewithasinglemicro-instruction,thatis,eachmicro-programconsistsofasinglecontrolword.Thisdesigncanbeasfastandasefficientashard-wiredcontrol,andallowsdesignerstobenefitfromtheadvantagesofmicroprogramming.Използване на твърд кабелен контролmakestheRISCsystemcontrollersimple.Thesimplicityofthedesignmakesthelayoutofthemachinemorereasonable,allowingthedesignertoconcentrateonoptimizingtheremaining,few,butcriticalprocessorfeatures.Thesimplifiedstructurerelievestheshortageofarearesourcesonthechip.Somestructuresthatarecriticaltoperformance,suchaslargeregistercomponents,conversionlookupbuffer(TLB)Scoprocessor,andmultiplicationanddivisionunitcanallbeinstalledonthesamechip..Theseadditionalresourcesaddagreatperformanceadvantagetotheprocessor.Infact,RISCdoesnotnecessarilyhavetheabovecharacteristicsstrictly,andsomesystemscalledRISCevenviolatesomeoftheaboveaspects.TheabovecharacteristicsshouldbeusedasaguidingprincipletoexplainthenatureofRISC.Torelax,asystemthatsatisfiesmostofthesecharacteristicscanberegardedasaRISC.

Предимства

RISC може да подобри скоростта, като същевременно поддържа ниски разходи.

ApplicableVLSI(VERYLARGESCALEINTEGRATION)process.

BecausetheRISCinstructionsetisclearandsimple,itonlyneedsarelativelysmallandsimplecontrolunitdecodingandhardwareexecutionsubsystem.ThisleadstothefollowingresultswhenusingVLSItoimplementcomputersystems:

Чипарът, зает от контролната единица, е значително намален. Например, RlsCI представлява 10%, докато CISC обикновено представлява повече от 50%.. Следователно в чипа RISCVLSI остава повече свободно пространство, така че целият процесор и други компоненти са на един чип (като кеш, единица с плаваща запетая, част от основната памет, 1/0 порта).

Becausethecontrolareaisreduced,itispossibletoincreasetheamountofCPUregisters(138forRISCI)onthechip.

ByreducingtheareaofthecontrolunitontheVLSIchipandplacingalargenumberofconsistentregisters,theregularizationfactor(regulariZationfaetor)ofthechipcanbeimproved.Basically,thehighertheregularizationfactor,thelowertheVLSIdesigncost.

ItisbeneficialtouseGaAs(galliumarsenide)VLSIchipimplementationtechnology,becauseitissuitableformanufacturinghigh-densitychips.Inshort,itreducesthecomplexityoftheprogramandsimplifiesthestructure.

Висока скорост.

OneofthecharacteristicsofRISCistheinstructionpipeline,andtheconsistencyofinstructionlengthandexecutiontimeminimizesthewaitingandholdingtimeinthepipeline.Thesefactorshelpincreasethecalculationspeed.ThesimplerandsmallercontrolunitinRISCalsohasfewerdoors,whichmakesthesignaltransmissionpathofthecontrolunitshorterandspeedsuptheoperation.Thesimplificationoftheinstructionsetresultsinasmallandsimpledecodingsystem,whichcanspeedupthedecodingspeedofRISC.ThereductionofcontrolunitsbyhardwiringmakesRISCperformfasterthansystemsusuallycontrolledbymicroprograms.TherelativelylargeCPUregisterreducestheconflictsbetweenCPUandmemoryinfetchinginstructionsandstoringnumbers;thelargeregistergroupcanbeusedtostoretheparameterspassedbetweenthecallingprocessandthecallingprocess,andstoretherelevantinformationoftheinterruptprogram,otherwise,Thisinformationcanonlybestoredinmemory.Allthesesavealotofcomputerprocessingtime.Thebranchdelaytechniqueinoptimizingcompilationalsocontributestotheincreaseinspeed.Ingeneral,RISCisgenerally2to4timestheprocessingspeedofCISCwhenthefunctionsareroughlythesame.

Намалени разходи за проектиране и подобряване на надеждността

CPUisrelativelysmallandsimplecontrolunitItusuallyleadstothefollowingcostandreliabilitybenefits:a.ThedesigntimeoftheRISCcontrolunitisshortened,whichcanreducetheoveralldesigncost.b.Theshortdesigntimereducesthepossibilityofthefinalproductbeingdiscardedwhenthedesigniscompleted.c.Simpler,smallercontrolunitcanreducedesignerrors,therebyimprovingreliability;moreover,itiseasiertolocateandcorrecterrorsthanCISC.d.Becausetheinstructionformatl(or2types)issimpleandfew,allinstructionshaveastandardlength,sotheinstructionwillnotcrossthewordboundary,norwillitcrossdifferentpagesinthevirtualmemory(iVrtualMemory),whichexcludesvirtualmemorymanagementPotentialdifficultiesinsubsystemdesign.

Поддържа език на високо ниво, но не и език за сглобяване

TheevolutionfromCISCtoRISCTheprocessissimilartothedevelopmentprocessofassemblylanguagetohigh-levellanguage.Writingaprograminassemblylanguageneedstousesomewell-designedcomplexinstructions,whilewritingahigh-levellanguageisalmostdifferentfromcomplexinstructions.Whilepursuingstreamlinedinstructions,RISCcloselyintegratesthedesignofthearchitectureandoptimizedcompilation,sothattheintegratedresultsleadtotheimprovementofoverallperformance.IfthedevelopmentofRISCisbasedontheimprovementofVLSItechnologyandcompilationtechnology,itcanbeunderstoodasreplacingthecomplexinstructionsystemwithcomplexcompilation,anditcanevenberegardedasthetransferofhardwareproblemstosoftware.Inrecentyears,therapiddevelopmentofintelligentcompilerscaneasilyperformthistask.PerhapstheadvantageofRISCliesinthis.TraditionalCISCmusthavecomplicatedmicrocodewritinganddesignwork,andtheuseofassemblylanguagealsoinvolvesthedevelopmentofassemblyprograms,whichareverylabor-intensiveandtime-consuming.RISCismoreconducivetosupportinghigh-levellanguages,whichisalsooneofthewaystosolvethe"softwarecrisis"facedbycomputersforalongtime.ThesuccessofRISCliesinsoftwarecompatibility.Aslongasthesource-levelcompatibilityismadethroughrecompilation,theexistingsoftwarecanbeeasilyrunontheRISCmachine.

Ползи за програмисти (потребители)

ThesimplifiedstructureenablesprogrammersAlsogotmanybenefits:

Повече унифицирани инструкции са много удобни за използване.

Sincethereisarelativelystrictcorrespondencebetweenthenumberofinstructionsandthenumberofcycles,theactualeffectofcodeoptimizationcanbeeasilymeasured.

Програмистите имат по-точно разбиране на хардуера.

Недостатъци

Thereisanupsurgeinthecomputerworldtofindbetterperformance.RISCandCISCarebothconfrontingandcomplementary.RISChasitsownshortcomings.

Thelengthoftheinstructionsaftercompilationislonger,andthememoryneedstobelarger

TheshortcomingsofRISCaredirectlyrelatedtosomeofitsadvantages.BecauseRISChasasmallnumberofinstructions,somefunctionsthatcanbecompletedbyonlyoneinstructioninCISCrequiretwo,threeormoreinstructionsinRISC,whichmakestheRISCcodelonger,soRISCprogramsrequiremorememory.InstructionconflictsbetweenmemoryandCPUwillalsoincrease.Researchshowsthat,onaverage,toperformthesamefunction,aRISCprogramis30%longerthanaCISCprogram.Atthesametime,RISChashigherrequirementsforcompilers.Thedesignofoptimizingcompilersisaverycomplexandtechnicallydemandingwork.ItmustbecompiledbytheRISCmachinemanufactureritself,becauseitisimpossibletogenerateacompilationwithoutdetailedRISCoriginaldata.Theobjectcodeoftheprogram.Inthisway,itismoredifficultforthird-partycompaniestoprovidenewversions,usershavelesschoice,andsoftwarecostsincrease.

Largeregisterbankmakesaddressingcomplicatedandslowsdown

AcontroversialfeatureofRISCsystemisitslargeregisterbank.Thelargeregisterbankhastheaforementionedadvantages,butontheotherhand,therearealsodisadvantages.Thelargeregisterincreasestheaddressingtime.Ontheotherhand,somecompilersmaketheuseofthesmallregisterbankmoreeffective.HowbigtheCPUregisterbankshouldberemainstobediscussed,andthelargeregisterUbankcanalsobereplacedbyacache(CACHE).Theshortcomingsofthelargeregisterbankcanbesummarizedasfollows:

Дълго време за достъп.

Там регистърната банка заема повече чипове.

Advancedcompilationtechnologymakesthesmallregisterbankmoreeffective.

IfallCPUregistersinthecontextswitchscenearesaved,thelargeregisterbankwillsavemorestoragetime.

Ifawindowpointerisused(oneofthekeypointsintheimplementationofRISCistooverlaptheregisterwindow,thepurposeistofacilitateparametertransfer.Theoverlapregisterwindowneedstousethewindowpointer),registeraddresstranslationThecodewillbelonger.Atthesametime,overlappingregistersalsocomplicatetheCPUlogic.

Управлението с твърд кабел не е гъвкаво

Thereisagreaterpossibilityoferrors,anditisnoteasytofindandmodifyerrors,anddealwiththemComplexinstructionsarealsomoredifficult.(4)Single-wordinstructionscannotusedirectmemoryaddressingforfull32-bitaddresses.Forthisreason,somemanufacturershavemadeasmallnumberofinstructionswithdouble-wordcards(suchasINTEL80960).Theuseofsuchinstructionsisuptotheprogrammertowritecompleteprogramswithonlysingle-wordinstructions.

Перспективи за развитие

ThebasicstartingpointofRISCtechnologyistoreducethecomplexityofhardwaredesignandincreasethespeedofinstructionexecutionbystreamliningthemachineinstructionsystem.AlthoughRISC'sdesignideashavehadahugeimpactonthecomputerstructureandachievedgreatsuccess,thecomplexinstructionsetcomputer(CISC)technologymakestheprogrammingoftheprogramrelativelyeasier.Therefore,theCISCtechnologyandtheRISCtechnologyarenotcompatible.Theyarenotisolatedfromeachother.Atpresent,thereisanewdesignidea,whichisbasedonimprovingtheperformanceoftheentirecomputersystem,andhasabsorbedtheadvantagesofCISCandRISCinstructure.Forexample,RISCtechnologyisusedinmanyCISCdesigns.TheNSC32532microprocessorofNationalSemiconductorCorporationadoptsRISCtechnologyinCISCdesign,whichreducestheaverageexecutiontimeofinstructionsfromtheoriginal6machinecyclestolessthan2.4machinecycles.Underthemainfrequencyof26MHZ,theoperatingspeedcanreach10-12M1PS.Intel80486andMot.r.la68040alsoabsorbsRISCdesigntechnology,sothattheaverageexecutiontimeofeachinstructionislessthan2machinecycles.Fairchild'sClippermachineisa32-bitmicroprocessorthatintegratestheadvantagesofR1SCandCISCtechnology,anditsrunningspeedisashighas33MIPS.Therefore,thecurrenttwomainmethodsofdesigningprocessors(RISCandClSCtechnology)arenotcompletelyseparate.Theyarecomplementarytoeachother.Atpresent,peoplehavecombinedCISCtechnologyandRISCtechnologytoproposeawritableinstructionsetcomputer(WISC)structuredesign,andspecifythestrategicprinciplesofconcentratingtheadvantagesofRlscandClsc,nevertheless,itisstillafurtherreleaseofaRISCtechnicaldogbasedontheconceptofRlSC.

Atpresent,mostRISCprocessorshavereachedthegoalofexecutingoneinstructionpercycle(ieCPIratio),butthisisnotthelimit.SuperscalarandsuperpipelinetechnologyhaveappearedinRISCtechnology.Superscalartechnologyistomakethemicroprocessorexecuteseveralinstructionsinparallelinoneclockcycle,whilesuperpipelinetechnologyisthatthemainstreampipelinesegment(instructiondecodingandinstructionexecution)onlyoccupiesapartofoneclockcycle,sothatitcanstillbeSeveralinstructionsIntel8096areexecutedsimultaneouslyinoneclockcycle.Itusessuperscalartechnology,whichcanexecuteintegerinstructionsandfloatingpointinstructionsatthesametime.IBM'sRS/6000alsousesasuperscalarstructure,theprocessorcontainsthreedifferentprocessingcomponents:fixed-pointprocessor,floating-pointprocessor,Branchprocessor,oneclockcyclecanexecutefourinstructions(4IPC),upto6IPc.RIScscientistspointedoutthattheencouragingprocessofimprovingmicroprocessorperformanceinthepastisunlikelytocontinue.Inthefuture,Cachecapacityanditsstructureandoptimizedcompilerwillbecomekeyfactorsinimprovingcomputerperformance.Thefocusoffuturedevelopmentwillbeonmulti-processortechnology.