Дизайнът включва

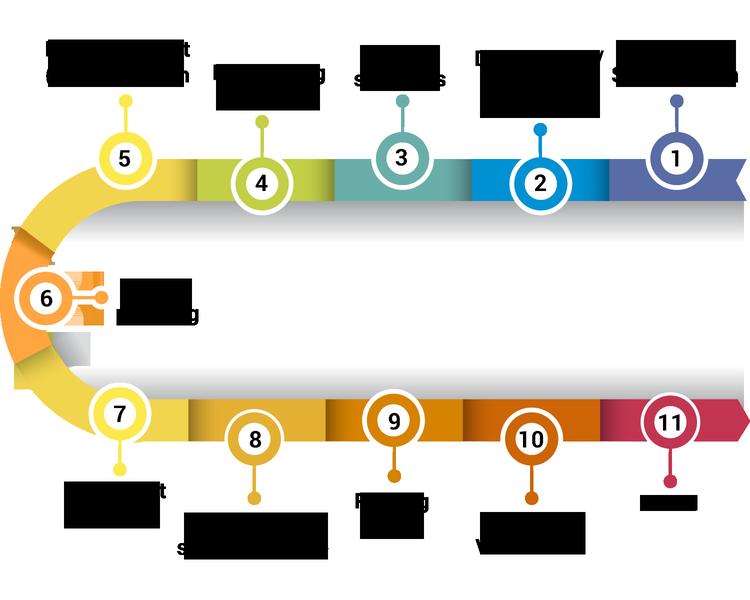

Theflowofintegratedcircuitdesigngenerallyfirstneedstobedividedintosoftwareandhardware,andthedesignisbasicallydividedintotwoparts:chiphardwaredesignandsoftwareco-design.Chiphardwaredesignincludes:

1. Етап на функционален дизайн.

Designer’sproductapplicationoccasions,setsomespecificationssuchasfunction,operatingspeed,interfacespecifications,environment

environmenttemperatureandpowerconsumption,etc.,asafuturecircuitdesigninaccordancewith.Itcanfurtherplanhowsoftwaremodulesandhardwaremodulesshouldbedivided,whichfunctionsshouldbeintegratedintheSOC,andwhichfunctionscanbedesigned

изчислено на платката.

2.Описание на дизайна и проверка на ниво на поведение

Afterthefunctiondesigniscompleted,theSOCcanbedividedintoseveralfunctionalmodulesaccordingtothefunction,andtheIPcoresthatwillbeusedtoimplementthesefunctionsaredetermined.

ThisstageindirectlyaffectstheinternalstructureoftheSOCandtheinteractivesignalsbetweenvariousmodules,aswellasthereliabilityoffutureproducts.

Afterdecidingthemodule,youcanusehardwaredescriptionlanguagesuchasVHDLorVerilogtorealizethedesignofeachmodule.

Then,usethecircuitsimulatorofVHDLorVerilogtoverifythedesign(function

симулация, или симулация на поведение).

Notethatthiskindoffunctionalsimulationdoesnotconsidertheactualdelayofthecircuit,norcanitobtainaccurateresults.

3.Логически синтез

Afterconfirmingthatthedesigndescriptioniscorrect,youcanusethelogicsynthesistool(synthesizer)forsynthesis.

Inthesynthesisprocess,youneedtoselecttheappropriatelogiccelllibraryasareferencewhensynthesizinglogic

вериги.

Thewritingstyleofthehardwarelanguagedesigndescriptionfileisanimportantfactorthatdeterminestheexecutionefficiencyofthesynthesistool.

Infact,theHDLsyntaxsupportedbysynthesistoolsislimited,andsometooabstractsyntax

isonlysuitableasasimulationmodelforsystemevaluationandcannotbeacceptedbysynthesistools.

Logicsynthesis getsthegate-levelnetlistlist.

4.Gate-LevelNetlistVerification

Gate-LevelNetlistVerificationisaregistertransfer-levelverification.Themaintaskistoconfirmwhethertheintegratedcircuitmeetsthefunctionalrequirements.Thistaskisgenerallycompletedwithagate-levelverificationtool.

Notethatthedelayofthegatecircuitneedstobeconsideredinthesimulationatthisstage.

5.Оформление и трасиране

Layoutreferstorationallyarrangingthedesignedfunctionalmodulesonthechipandplanningtheirlocations.Wiringreferstothewiringthatcompletestheinterconnectionbetweenmodules.Notethattheconnectionbetweeneachmoduleisusuallyrelativelylong,sotheresultingdelaywillseriouslyaffecttheperformanceoftheSOC,especiallyinthe0.25micronprocessandabove,thisphenomenonismoresignificant.Atpresent,thisindustryisstillavacancyinChina,andtherearestillrelativelyfewuniversitiesofferingintegratedcircuitdesignandintegratedsystems.Amongthem,schoolswithbetterteachersincludeShanghaiJiaotongUniversity,HarbinInstituteofTechnology,HarbinUniversityofScienceandTechnology,SoutheastUniversity,andXi’anElectronicTechnology.University,UniversityofElectronicScienceandTechnologyofChina,FudanUniversity,EastChinaNormalUniversity,etc.Thisfieldhasgraduallybecomesaturated,andthereisagrowingtrendtofollowthepathofthesoftwareindustryinthosedays.

Процес на проектиране

1.Проектиране на вериги

Completethecircuitdesignaccordingtothecircuitfunction.

2. Предварителна симулация

Simulationofcircuitfunctions,includingsimulationofpowerconsumption,current,voltage,temperature,voltageswing,inputandoutputcharacteristicsandotherparameters.

3. Дизайн на оформлението (оформление)

Drawthelayoutbasedonthedesignedcircuit.Cadencesoftwareisgenerallyused.

4. Пост-симулация

Simulatethedrawnlayoutandcompareitwiththeprevioussimulation.Ifitfailstomeettherequirements,thelayoutneedstobemodifiedorredesigned.

5. Последваща обработка

TheGDSIIfileisgeneratedfromthelayoutfileandsubmittedtoFoundryfortape-out.